莱芜关于网站建设的公司查图百度识图

目录

- 1、前言

- 2、目前主流的FPGA图像缩放方案

- 3、本方案的优越性

- 4、详细设计方案

- 5、vivado工程详解

- 6、上板调试验证并演示

- 7、福利:工程源码获取

1、前言

代码使用纯verilog实现,没有任何ip,可在Xilinx、Intel、国产FPGA间任意移植;

图像缩放的实现方式很多,最简单的莫过于Xilinx的HLS方式实现,用opencv的库,以c++语言几行代码即可完成,但大多使用了IP,导致在其他FPGA器件上移植变得困难。

本文详细描述了纯verilog实现设计方案,工程代码编译通过后上板调试验证,文章末尾有演示视频,可直接项目移植,适用于在校学生做毕业设计、研究生项目开发,也适用于在职工程师做项目开发,可应用于医疗、军工等行业的数字成像和图像传输领域;

提供完整的、跑通的工程源码和技术支持;

工程源码和技术支持的获取方式放在了文章末尾,请耐心看到最后;

关于HLS实现图像缩,放请参考我之前写的文章HLS实现图像缩放点击查看:HLS图像缩放

关于纯verilog实现图像缩放,请参考我之前写的文章纯verilog实现图像缩放点击查看:verilog图像缩放

本设计基于我之前写的文章纯verilog实现图像缩放开发;

2、目前主流的FPGA图像缩放方案

目前市面上主流的FPGA图像缩放方案如下:

1:Xilinx的HLS方案,该方案简单,易于实现,但只能用于Xilinx自家的FPGA;关于HLS实现图像缩放请,参考我之前写的文章HLS实现图像缩放点击查看:HLS图像缩放

2:非纯Verilog方案,大部分代码使用Verilog实现,但中间的fifo或ram等使用了IP,导致移植性变差,难以在Xilinx、Altera和国产FPGA之间自由移植;

3:纯Verilog方案,也就是本方案,一个字:牛逼!!!

3、本方案的优越性

一个字:牛逼,表现如下:

1:纯Verilog代码实现,学习性和阅读性达到天花板;

2:移植性达到天花板,Xilinx、Altera和国产FPGA之间自由移植;

3:算法达到天花板,融合了邻近插值和双线性插值两种算法;

4:实用性达到天花板,采用串口协议帧控制切换,不同于市面上验证性和实验性的工程,本设计直接面向实用工程,贴近真实项目,由串口控制缩放分辨率,做类似项目的兄弟可直接拿去用,一个月工资直接拿到手。。。

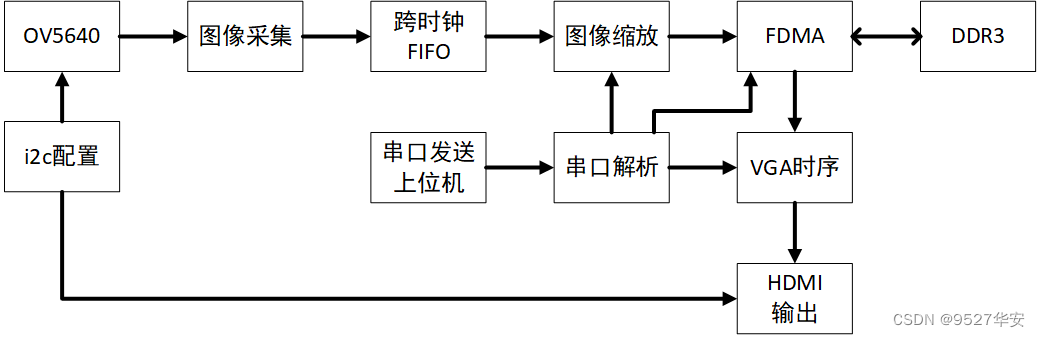

4、详细设计方案

图中使用到了HDMI输出,HDMI输出由silicon9134芯片驱动,关于这部分请参考我之前写的文章点击查看:silicon9134驱动HDMI输出

图中使用到了FDMA做图像缓存,关于这部分请参考我之前写的文章点击查看:FDMA图像缓存

关于纯verilog实现图像缩放,请参考我之前写的文章纯verilog实现图像缩放点击查看:verilog图像缩放

那篇文章详细描述了纯Verilog实现任意尺寸图像缩放的方案,本设计也是基于那个工程修改了,增加了适用于真实项目的串口控制功能,这里只讲新增部分的设计方案;

关于串口协议帧部分,请参考我前面写的文章串口协议帧

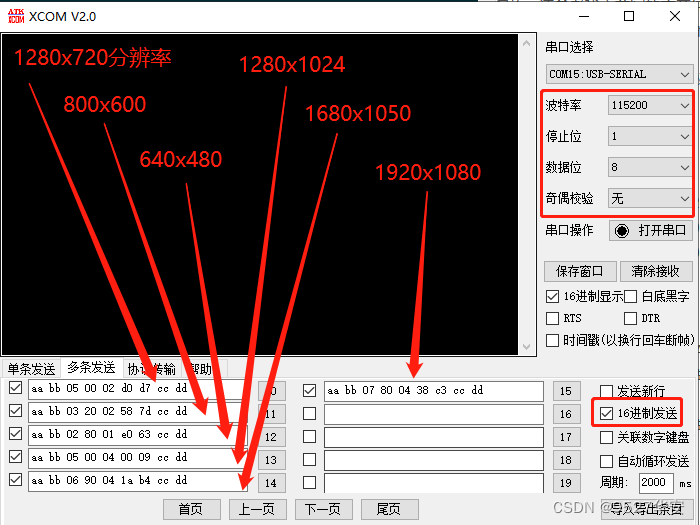

串口协议帧控制缩放分辨率协议如下:

有效数据的高两个字节决定输出分辨率的宽;

有效数据的低两个字节决定输出分辨率的高;

比如:

有效数据0x05,0x00,0x02,0xd0表示输出1280x720的视频;

有效数据0x03,0x20,0x02,0x58表示输出800x600的视频;

有效数据0x07,0x80,0x04,0x38表示输出1920x1080的视频;

具体操作如下:

上电后默认输出原图分辨率为1280x720;

串口发送指令控制缩放模块逻辑如下:

串口指令分辨率参数同时传递给图像缩放模块、FDMA和VGA时序模块;

如果串口指令分辨率小于原图,则控制图像缩放模块做缩小操作;将缩小后的分辨率给FDMA将制定分辨率的图片写入DDR3缓存后输出,同时VGA时序模块只输出制定大小的有效图像,即缩小后的分辨率图像;

如果串口指令分辨率大于原图,则控制图像缩放模块做放大操作;将缩小后的分辨率给FDMA将制定分辨率的图片写入DDR3缓存后输出,同时VGA时序模块只输出制定大小的有效图像,即放大后的分辨率图像;

下面给出串口指令发送举例:

串口切换部分代码如下:

always @(*) beginif(~pll_resetn) beginw_ddr_clk=cmos_pclk;disp_h='d1280;disp_v='d720; endelse if(r_rx_data==32'h050002d0) begin //1280x720w_ddr_clk=cmos_pclk;disp_h='d1280;disp_v='d720; endelse if(r_rx_data==32'h03200258) begin //800x600w_ddr_clk=cmos_pclk;disp_h='d800;disp_v='d600; endelse if(r_rx_data==32'h028001e0) begin //640x480w_ddr_clk=cmos_pclk;disp_h='d640;disp_v='d480; endelse if(r_rx_data==32'h05000400) begin //1280x1024w_ddr_clk=clk_hdmi;disp_h='d1280;disp_v='d1024; endelse if(r_rx_data==32'h0690041a) begin //1680x1050w_ddr_clk=clk_hdmi;disp_h='d1680;disp_v='d1050; end else if(r_rx_data==32'h07800438) begin //1920x1080w_ddr_clk=clk_hdmi;disp_h='d1920;disp_v='d1080; endelse begin //1280x720w_ddr_clk=cmos_pclk;disp_h='d1280;disp_v='d720; end

end

这里设置了5种不同的分辨率,有缩小也有放大,可以根据自身项目修改参数,自由配置;

5、vivado工程详解

开发板:Xilinx Artix7开发板;

开发环境:Vivado2019.1;

输入:OV5640摄像头,原始分辨率1280x720p;

输出:HDMI,1080P分辨率下的输出分辨率有效区域显示;

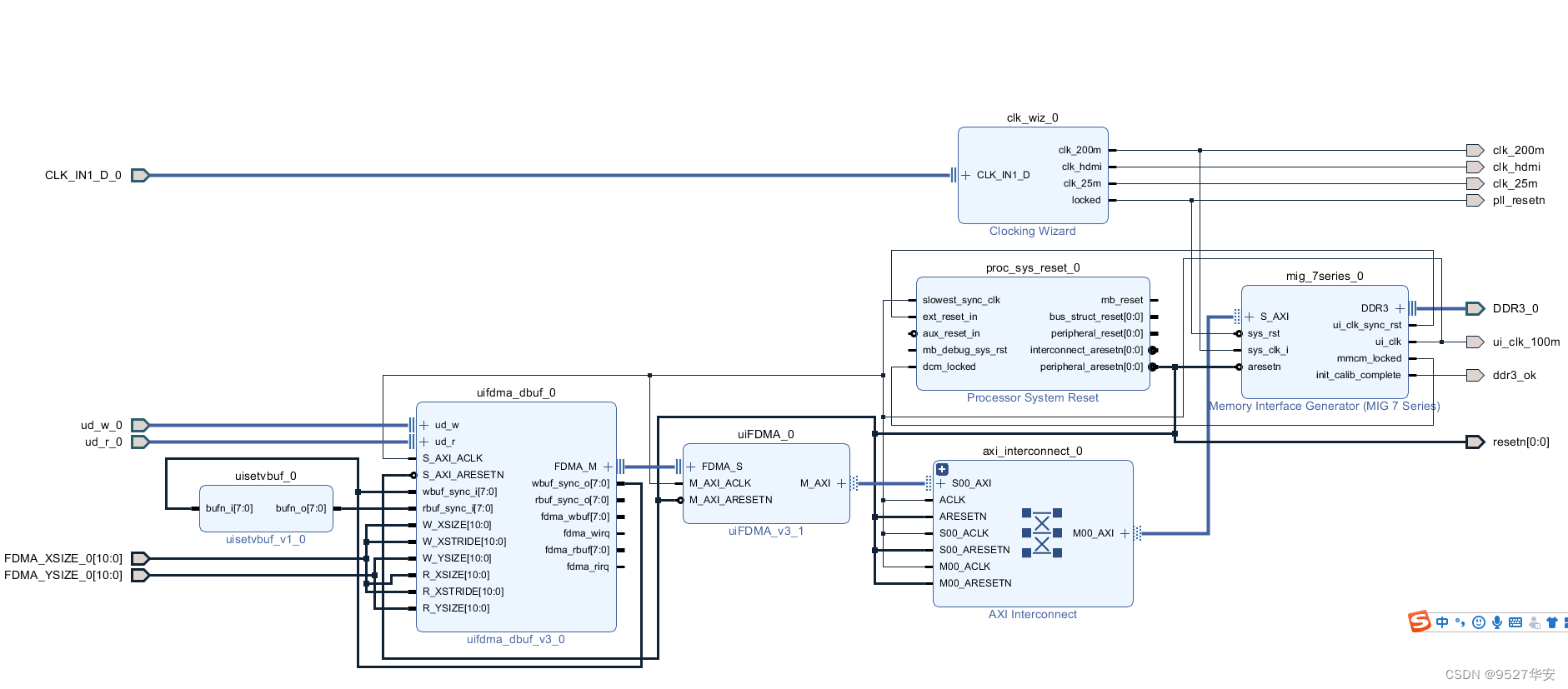

工程BD如下:

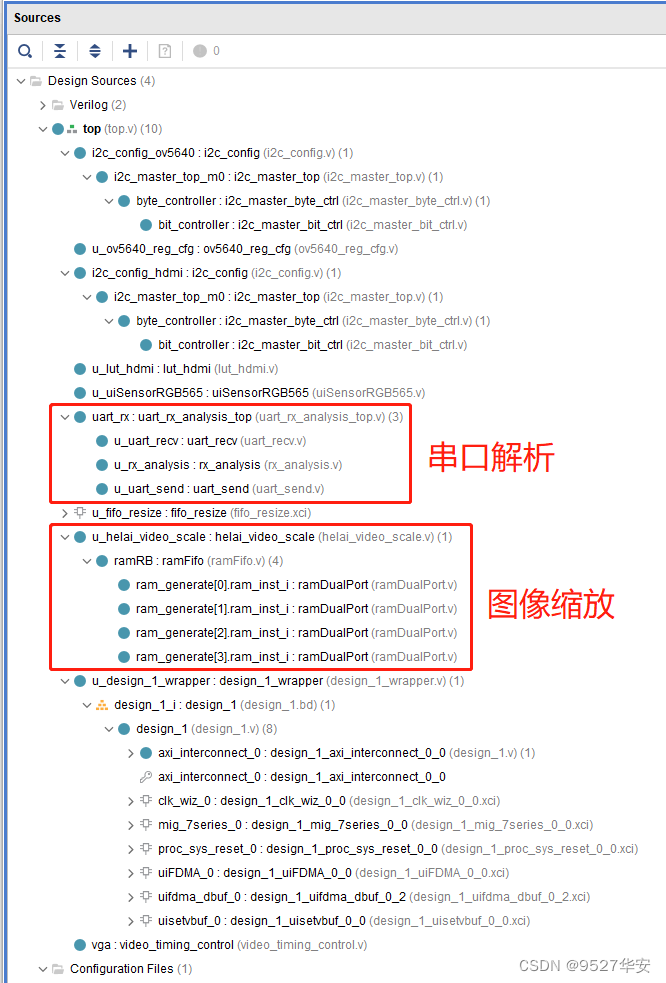

工程代码架构如下:

6、上板调试验证并演示

静态展示如下:

演示视频如下:

FPGA纯Verilog实现任意尺寸图像缩放,串口指令控制

7、福利:工程源码获取

福利:工程代码的获取

代码太大,无法邮箱发送,以某度网盘链接方式发送,

资料获取方式:私,或者文章末尾的V名片。

网盘资料如下: